IP Integrator这一块比较难配置,网上的教程比较乱,而且也少有针对AXIS Stream IP核专门配置的教程。所以我尝试着手把手的把配置过程在博客里展现出来。

我使用的开发板是ALinx AX7020,FPGA芯片zynq-xc7z020clg400-2。有些配置与我的板子是高度相关的,如果使用的是其他开发板请参照开发板提供商给的教程或参考资料配置。

1、创建Vivado项目。

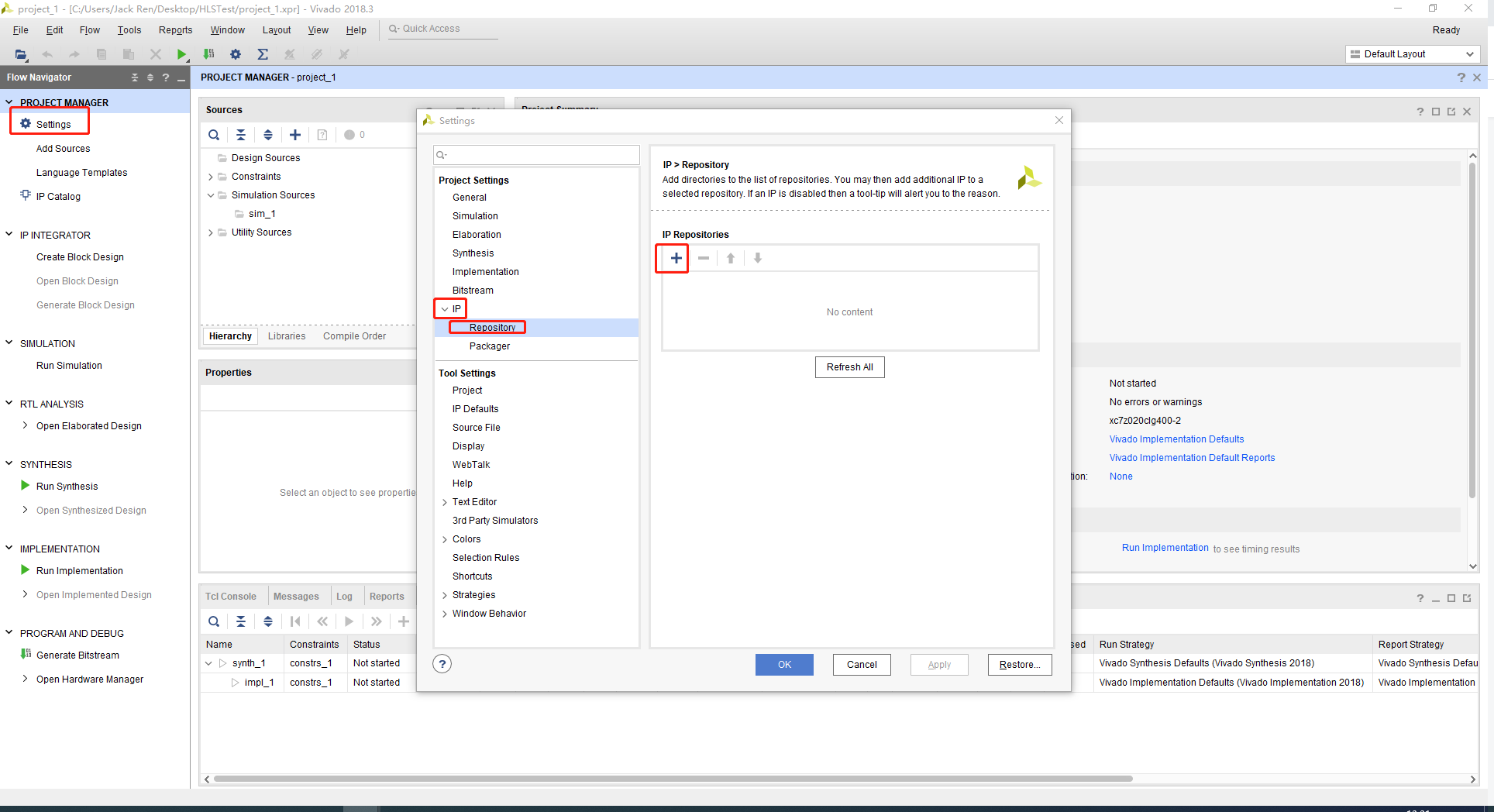

2、添加IP核扫描位置:Vivado左侧Flow Navigator——Project Manager——Settings——IP——Repository。点击+号选择你的HLS IP核所在的文件夹位置。一般来说,相对路径是solution/impl/ip。

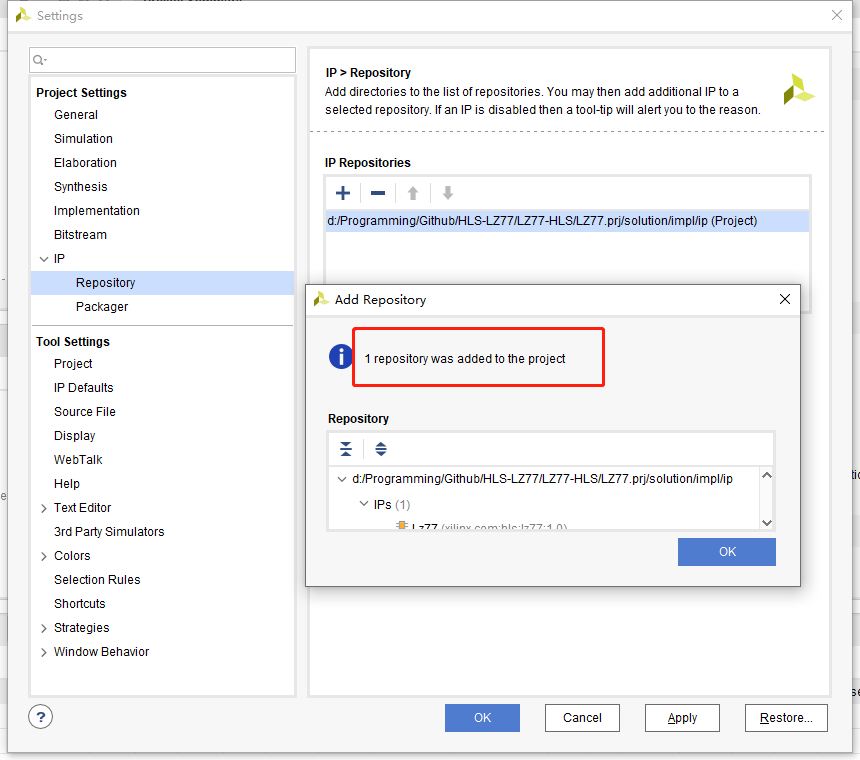

选择完毕后,弹出如下对话框,提示1个IP核已经成功添加。点击OK返回。

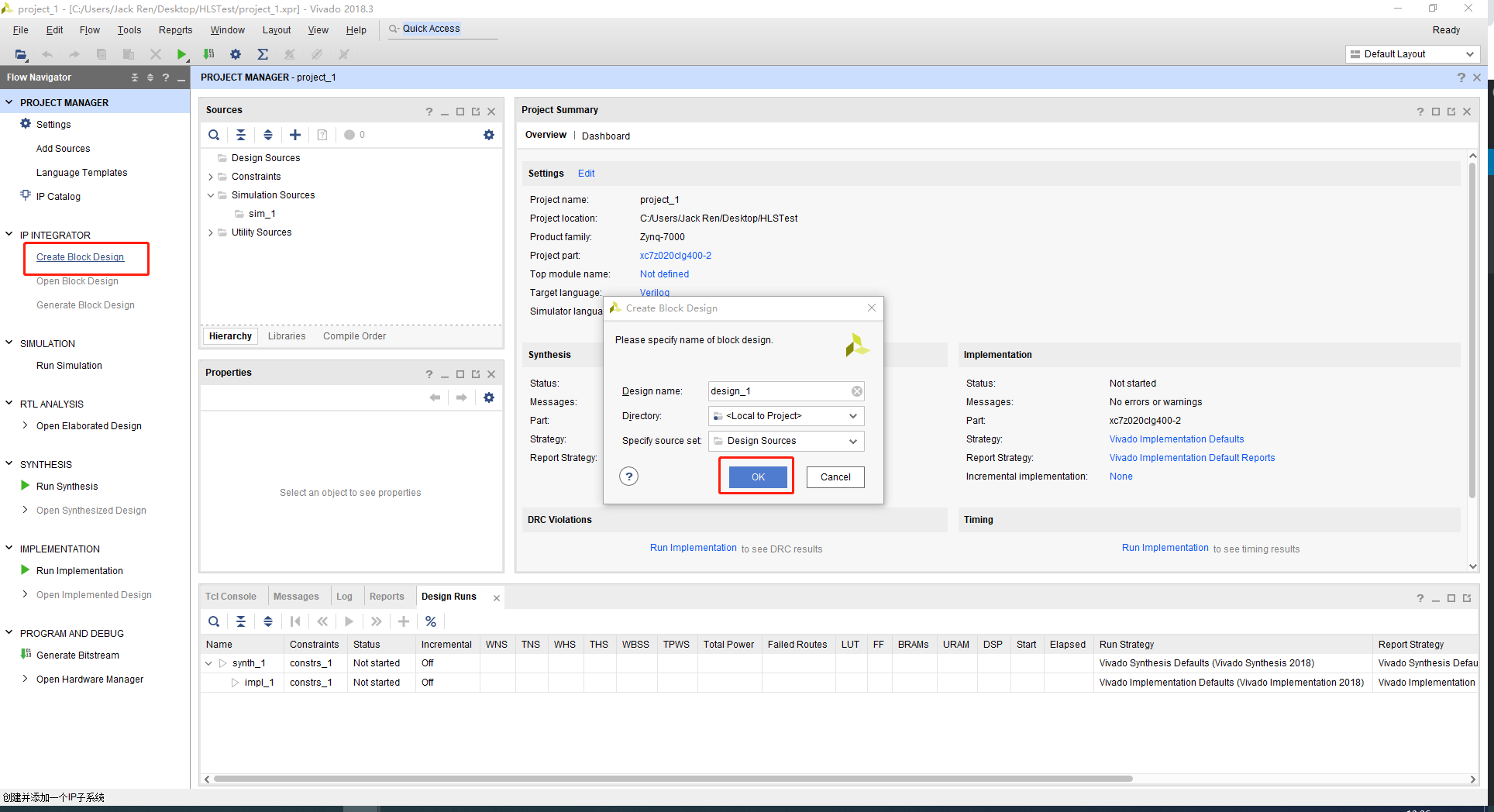

3、添加Block Design:Vivado左侧Flow Navigator——IP Integrator——Create Block Design,属性保持默认点OK。

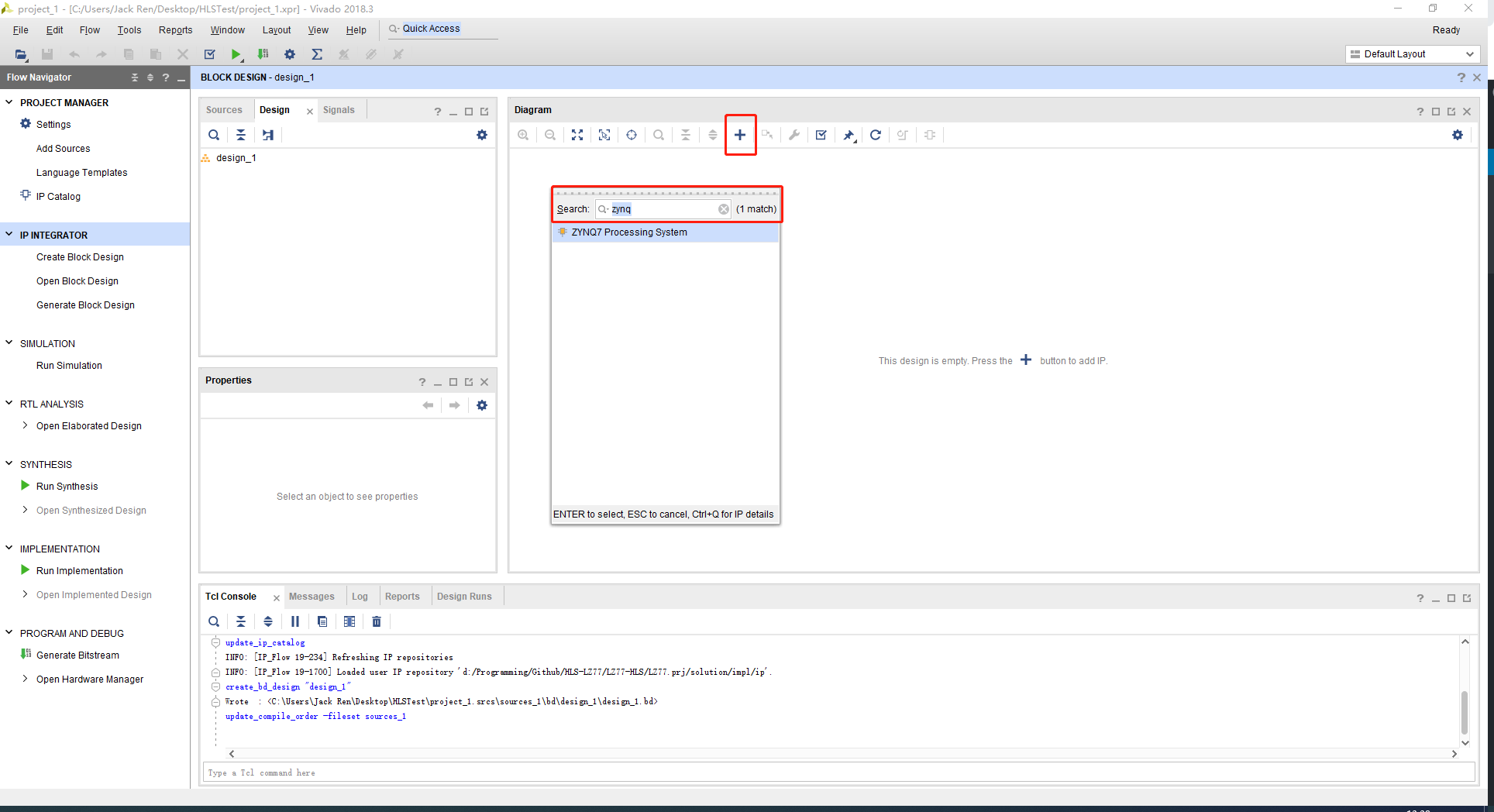

4、添加IP核:点击BLOCK DESIGN——Diagram——+号添加IP核。在方框中输入IP核名称。我们首先添加ZYNQ处理器系统。输入Zynq,点击唯一的一个Zynq7 Processing System就添加成功了。

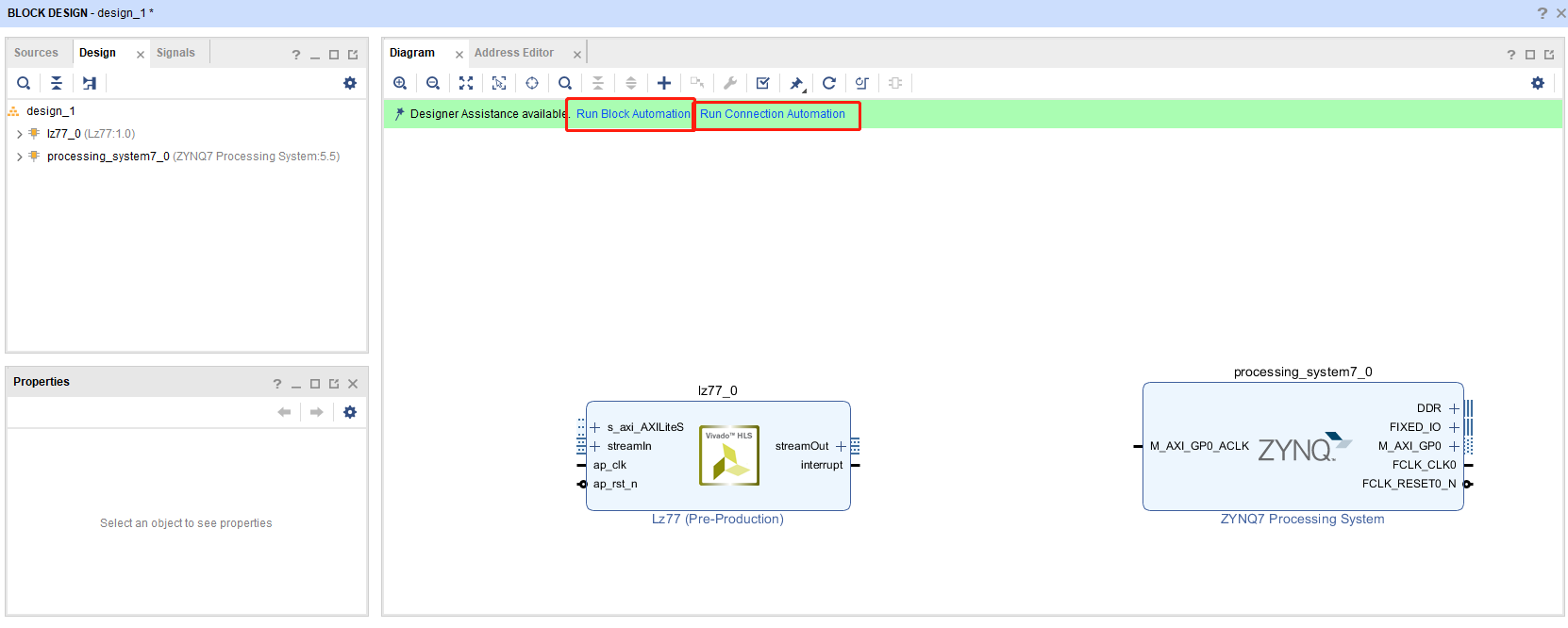

依此类推,我再添加自己自定义的IP核LZ77。此时上方弹出“Designer Assistance Available”,先后点击Run Block Automation和Run Connection Automation。弹出的对话框直接默认OK即可。

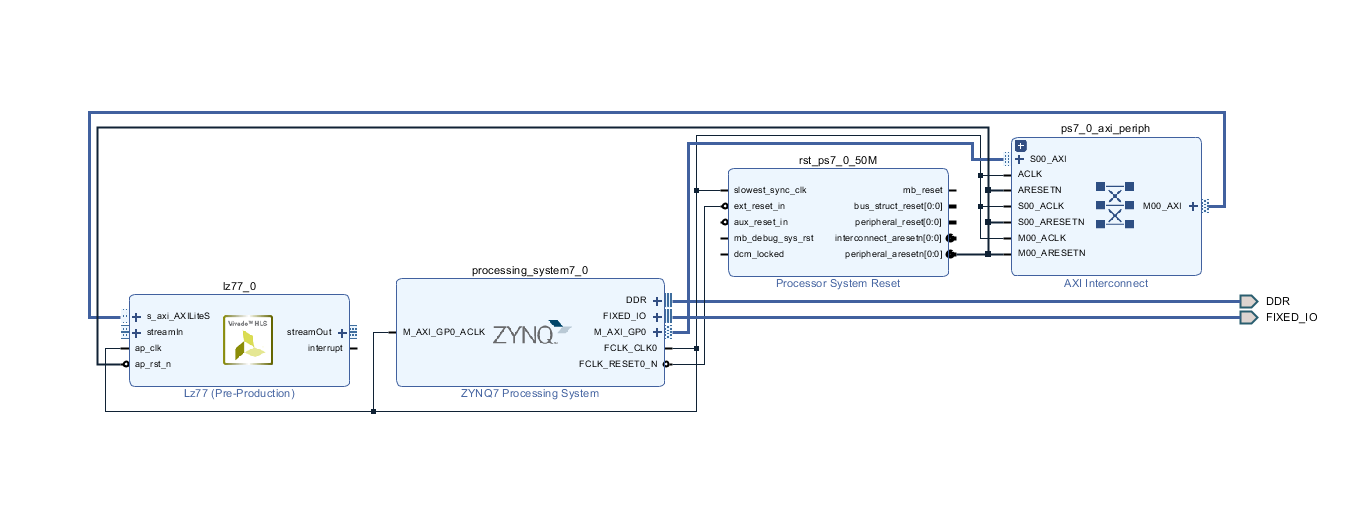

此时BLOCK DESIGN如下图:

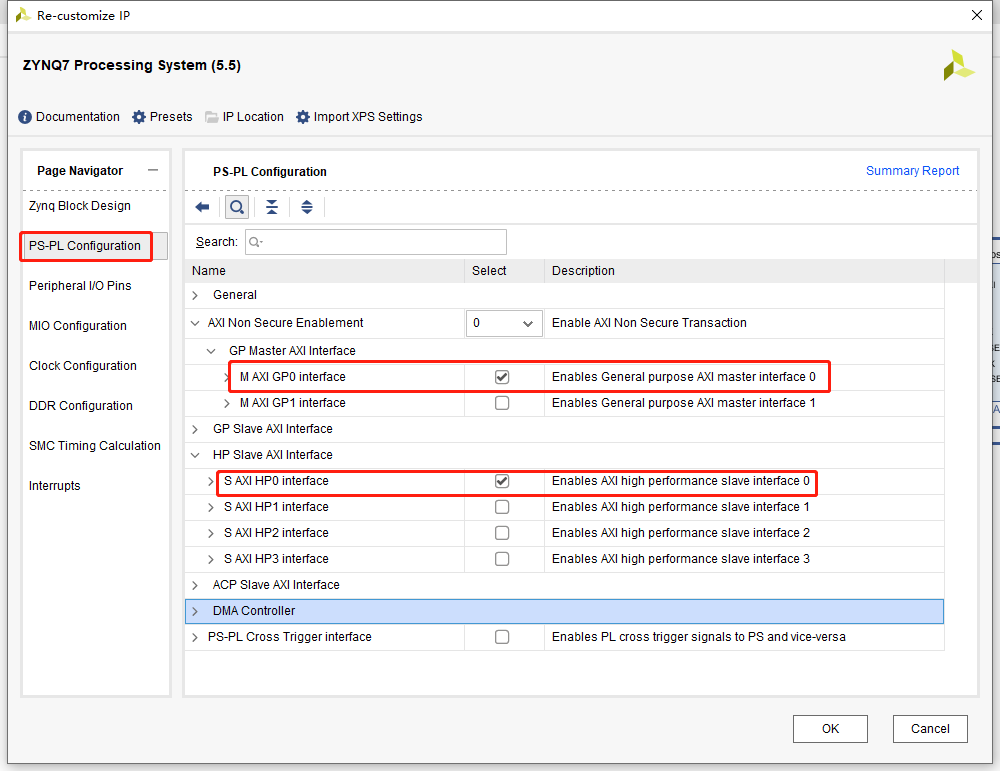

5、配置Zynq IP核,双击ZYNQ IP核进行配置:

点击Page Navigator——PS-PL Configuration。右侧勾选M AXI GP0 INTERFACE和S AXI HP1 INTERFACE。

其中M AXI GP0 INTERFACE用于PS和PL的一般AXI总线的数据交换,S AXI HP1 INTERFACE用于PS和PL的高速数据交换(AXI_STREAM)。

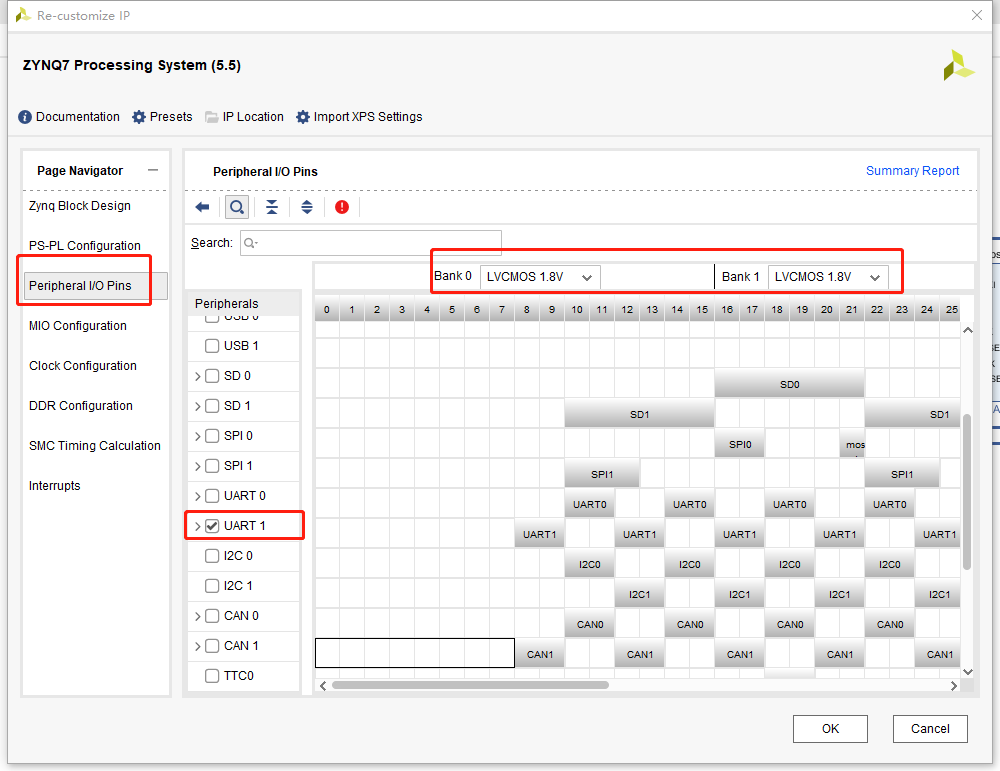

点击Page Navigator——Peripheral IO Pins。点击UART1开启板子上的串口,BANK0/1的电压都要调为LVCMOS 1.8V。从而使得串口可以正常工作。此处的设置是与你的板子类型相关的。如果有不清楚的地方可以去看你的板子制造商给的资料。

点击Page Navigator——DDR Configuration。Memory Part改为MT41J256M16 RE-125。内存类型与板子也是相关的。

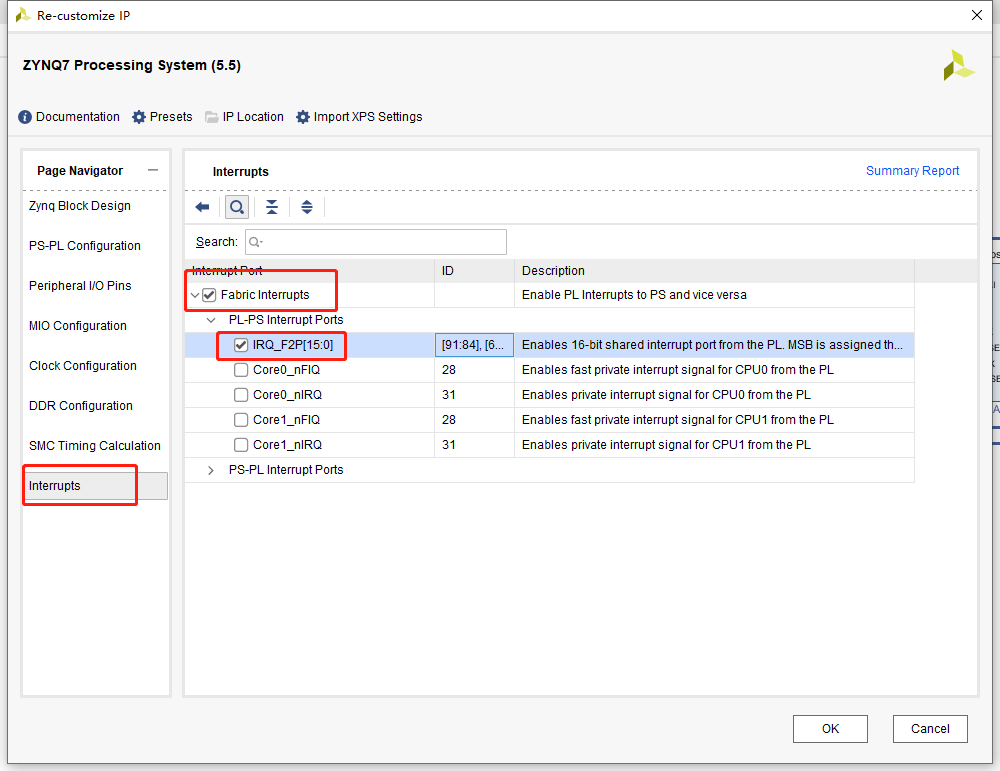

点击Page Navigator——Interrupt。先勾选Fabric Interrupts,再勾选IRQ_F2P。开启PL到PS的中断接收通道。

最后点击确定结束对Zynq IP核的设置。

6、添加DMA和AXI STREAM DATA FIFO IP核:

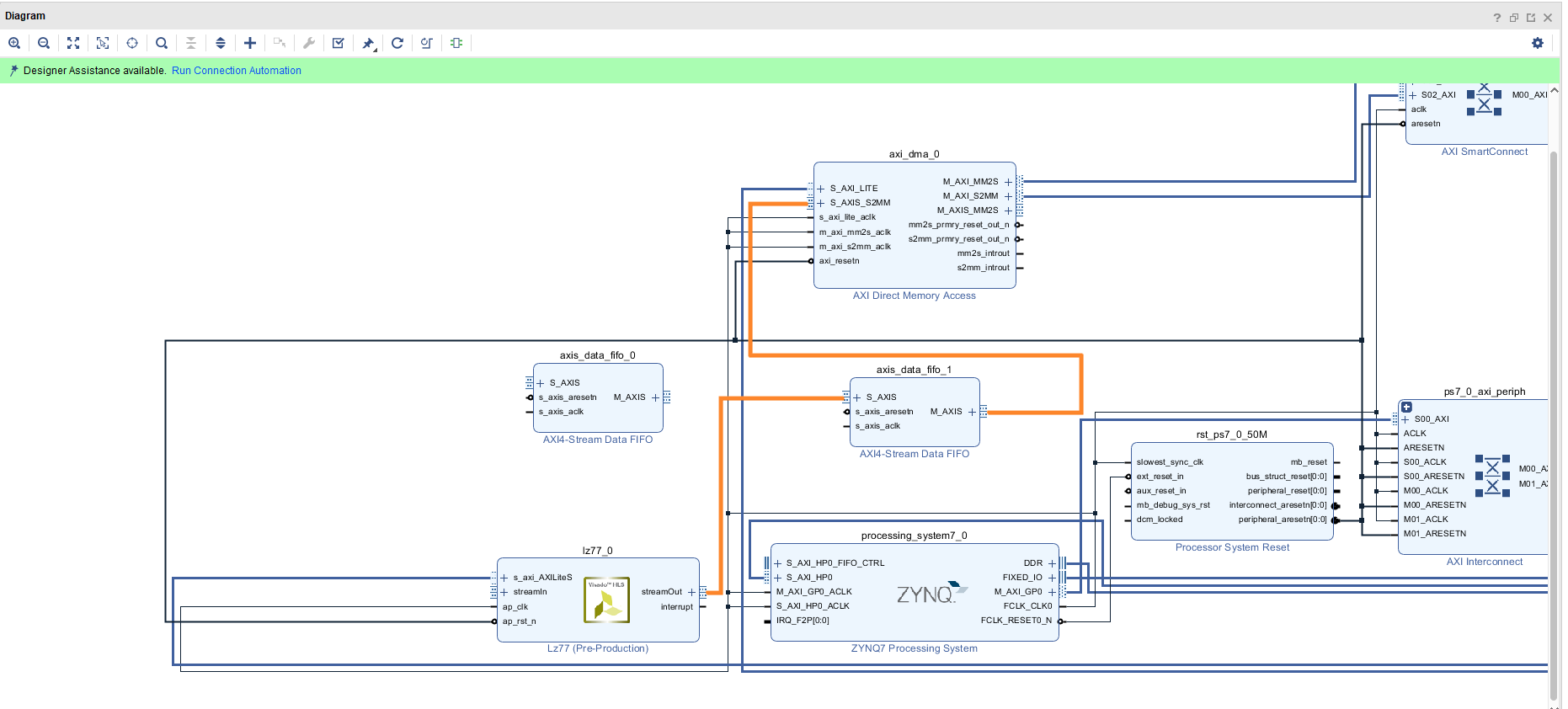

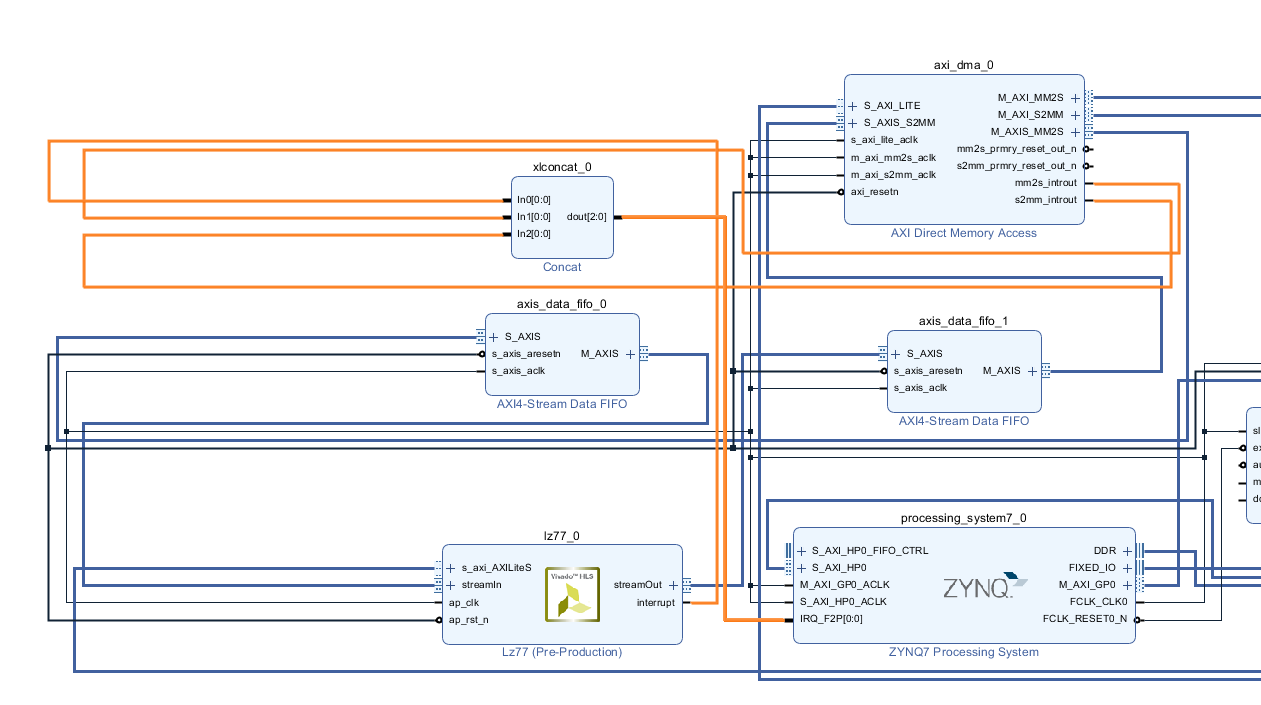

搜索AXI Direct Memory Access并添加一个。搜索AXI4-Stream Data FIFO并添加两个。进行两次Run Connection Automation。连线如下图:

7、配置DMA IP核:

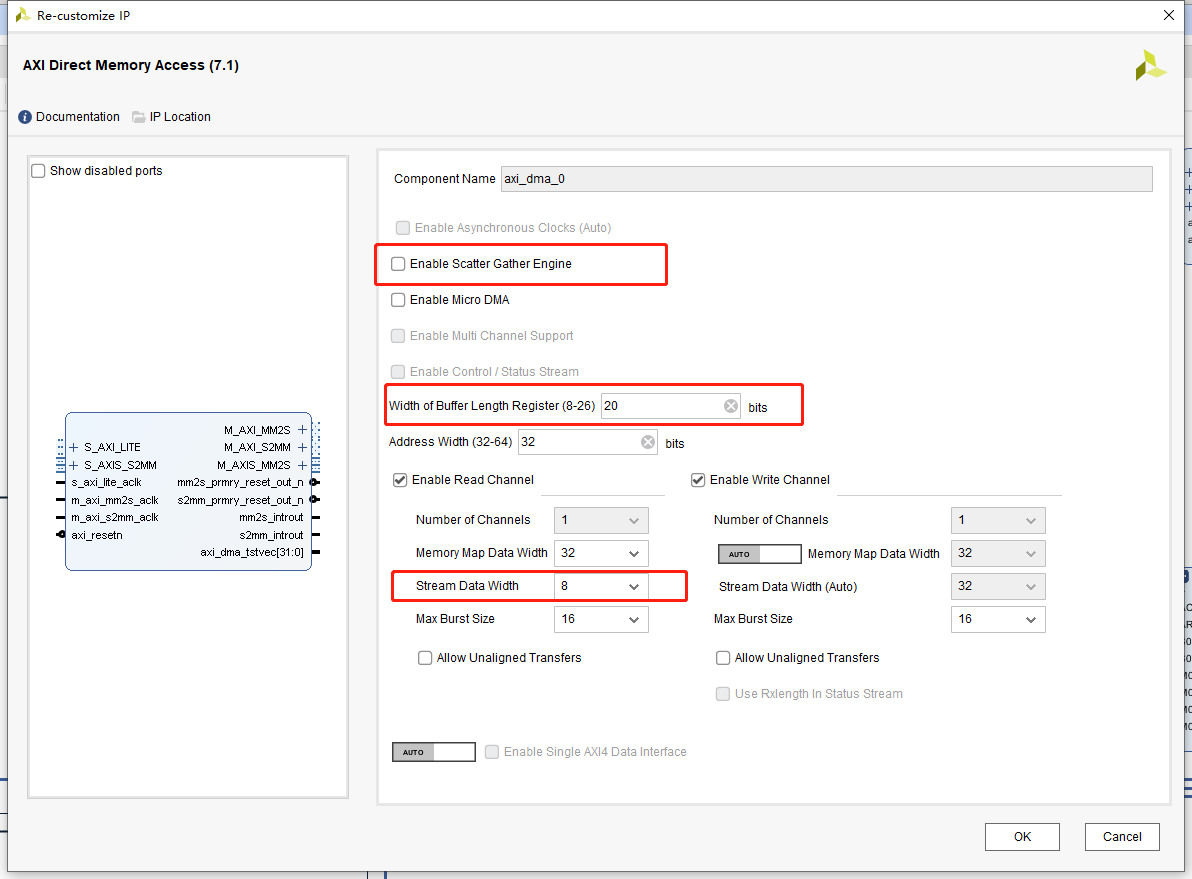

双击DMA,进入配置界面。取消勾选Enable Scatter Gather Engine。这是DMA IP核的高级特性,我们无需使用也不能使用。后面的SDK代码是与Scatter Gather Mode相冲突的。Width of Buffer Length Register适当调高即可,表示一次DMA请求最多可以传送多少数据(2的x次方个数据),Stream Data Width根据你HLS Stream传送数据的宽度自行设定,我的程序每次传送一个字节,因此设为8。

8、IP核、DATA FIFO与DMA的连线:

这里首先要明确的是MM2S和S2MM的意思:MM2S stands for Memory-Mapped to Streaming, whereas S2MM stands for Streaming to Memory-Mapped.

明确了之后,线就好连了。Vivado IP Integrator在连线的时候,哪个端口可以连,在上面会出现一个绿色的对勾,也可以用它来辅助判断。

因此对于PL端的IP核到PS端的数据流动,连接是:streamOut——S_AXIS——M_AXIS——S_AXIS_S2MM。图示如下:

对于PS端到PL端的IP核数据流动,连接是:M_AXIS_MM2S——S_AXIS——M_AXIS——streamIn。图示如下:

然后进行Run Connection Automation。

9、连接中断:

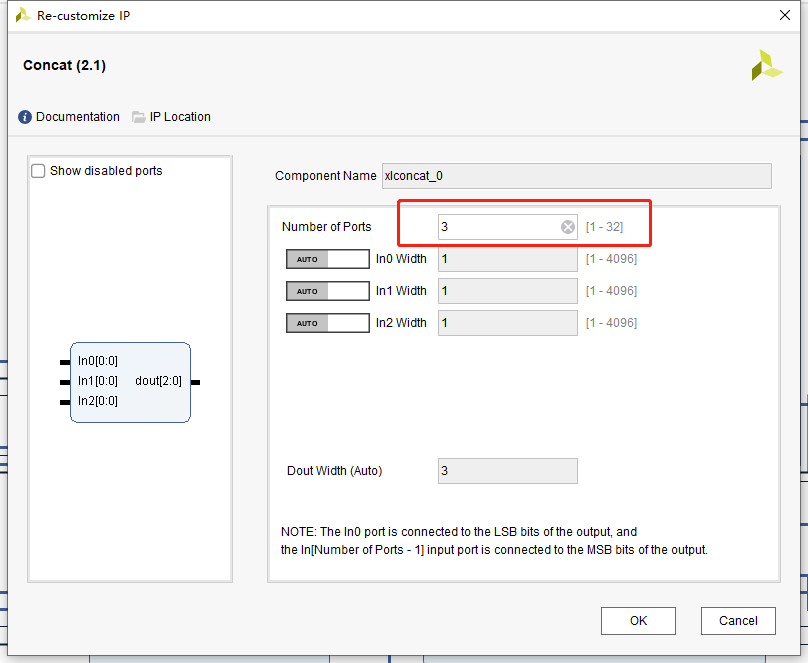

添加Concat IP核。对于本设计来说,有PL的LZ77 IP核需要中断(interrupt信号),还有DMA需要两个中断(mm2s_introut和s2mm_introut)。因此Concat的设置Number of Ports设为3。

把concat的出端连接到ZYNQ的IRQ_F2P。

连线后的图示如下:

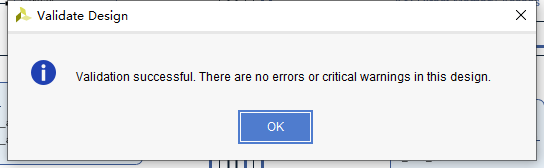

10、验证设计:

Vivado菜单栏——Tools——Validate Designs,或者F6,等待验证。应当出现如下对话框:

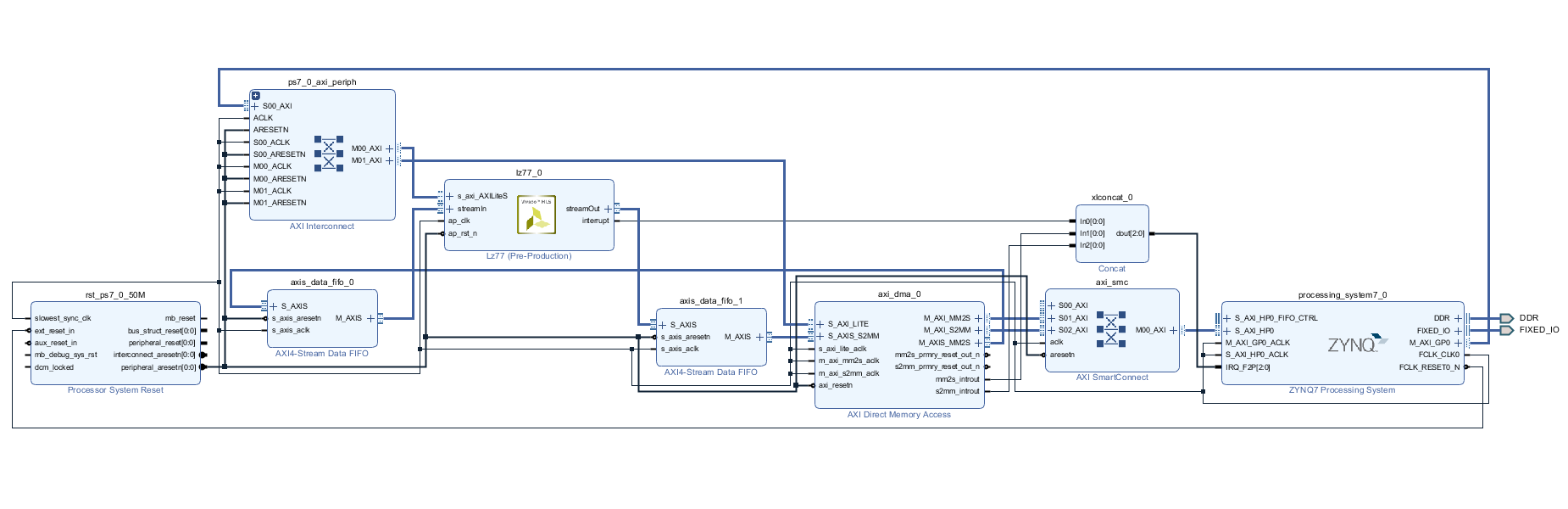

最后整体连线如下:

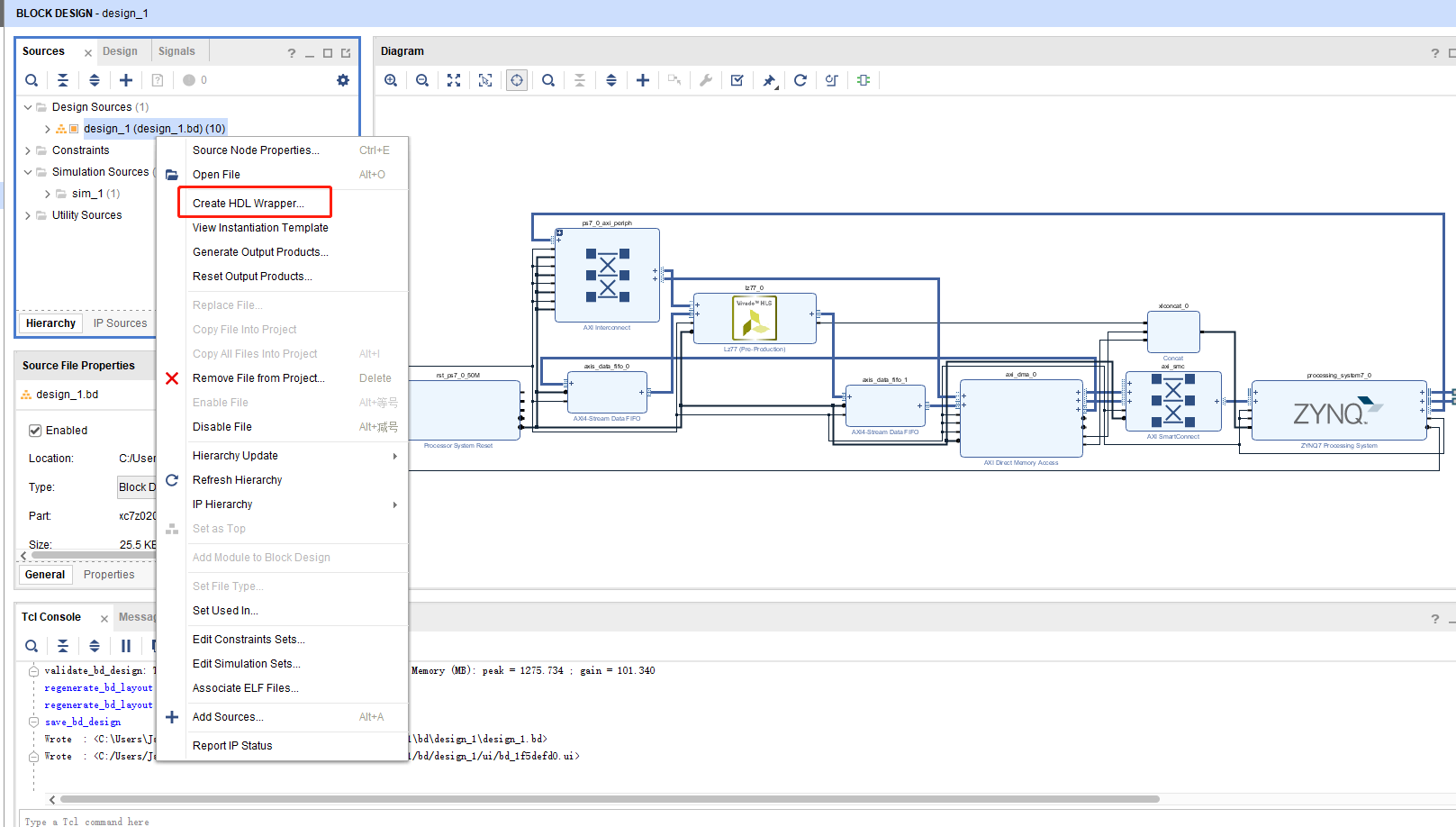

11、Create HDL Wrapper:默认选择OK即可。如果不创建HDL封装的话,它默认只是一个图形文件,无法综合。

12、综合、实现、生成Bitstream。

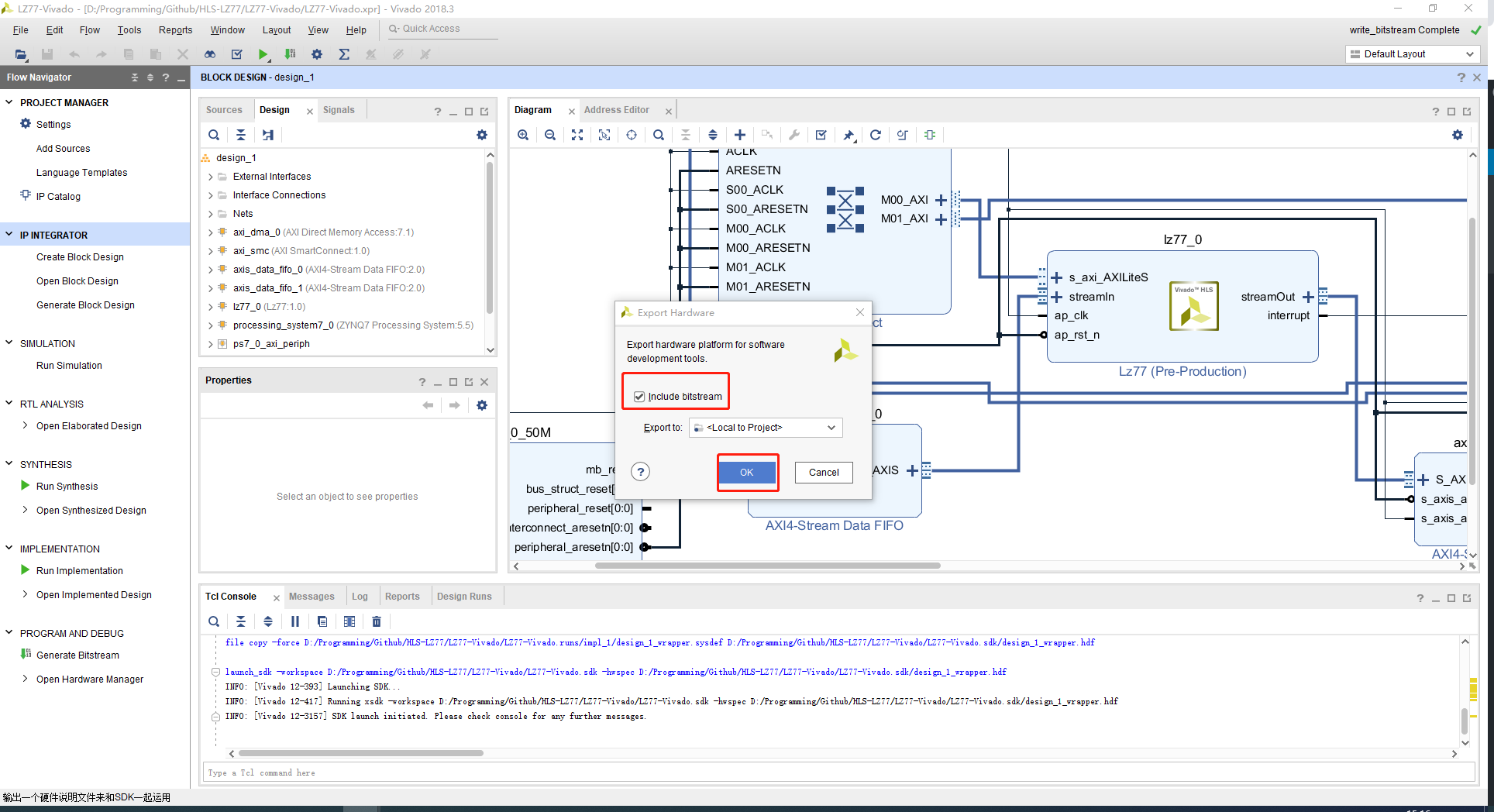

13、Vivado菜单栏File——Export——Export Hardware,勾选include bitstream。点击OK。

14、Vivado菜单栏File——Launch SDK,开发进入到PS阶段。

参考资料:

[1]: https://www.xilinx.com/support/documentation/ip_documentation/axis_infrastructure_ip_suite/v1_1/pg085-axi4stream-infrastructure.pdf

[2]: https://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html/

[3]: https://blog.csdn.net/m0_46498597/article/details/108648505

[4]: https://blog.csdn.net/long_fly/article/details/79702222

[5]: https://blog.csdn.net/q774318039a/article/details/88377135

[6]: https://blog.csdn.net/qq_20748649/article/details/50265141

[7]: https://blog.csdn.net/botao_li/article/details/86168384